# ARTICLE IN PRESS

Microprocessors and Microsystems xxx (2012) xxx-xxx

Contents lists available at SciVerse ScienceDirect

# Microprocessors and Microsystems

journal homepage: www.elsevier.com/locate/micpro

# A formal study on topology and floorplan characteristics of mesh and torus-based optical networks-on-chip

Kai Feng, Yaoyao Ye\*, Jiang Xu

Electronic and Computer Engineering Department, The Hong Kong University of Science and Technology, Hong Kong

### ARTICLE INFO

Article history: Available online xxxx

Keywords: Multiprocessor Optical network-on-chip Mesh Torus Floorplan

### ABSTRACT

The efficiency of collaboration among processors is a critical design metric for multiprocessor systemson-chip (MPSoCs). It is the communication architecture that determines the collaboration efficiency on the hardware side. Optical NoCs, which are based on optical interconnects and optical routers, offer a new approach to empowering ultra-high bandwidth with low power consumption. In this paper, we provide a detailed study on the floorplans of optical NoCs in two popular two-dimensional topologies: mesh and torus. The study covers important design metrics for mesh and torus-based optical NoCs, such as the number of waveguide crossings in the floorplan and the number of paths and hops. We summarize the results into equations, taking all the dimensional cases into consideration. Based on this study, as well as the properties of the XY routing algorithm, we propose several approaches to optimize the power efficiency of optical NoCs by minimizing the number of waveguide crossings in the floorplan. We show the optimization procedures for torus-based optical NoCs in all possible cases. Comparison results show that the floorplan optimization reduces waveguide crossings significantly within the entire network as well as in longest paths. As is suggested in this paper, the number of waveguide crossings represents power loss in the optical NoC. By minimizing the number of waveguide crossings in the optimized floorplans, the energy efficiency of the optical NoC is improved than the original designs.

© 2012 Published by Elsevier B.V.

# 1. Introduction

On-chip communications are facing new challenges in the gigascale multiprocessor system-on-chip (MPSoC) paradigm [1–3]. The number of transistors on a single chip has increased to billions or an even larger number because of the development of nanoscale CMOS technologies. Traditional on-chip communication techniques for MPSoCs have encountered several issues, such as poor scalability, limited bandwidth, and low utilization [4-6]. Networks-on-Chip (NoCs) were proposed to relieve these issues by taking advantage of modern networking theories for on-chip communications [1].

As semiconductor technologies continually scale the feature sizes down, metallic interconnects with limited bandwidth and high power dissipation are becoming the bottleneck of electronic NoCs. Traditional electronic NoCs may not satisfy the bandwidth and latency requirements of future gigascale MPSoCs within restricted power budget. Optical interconnections have demonstrated their strength in multicomputer systems, on-board interchip interconnect, and switching fabrics in core routers, etc. Optical NoCs (ONoCs), which are based on on-chip optical routers and optical interconnects, are a promising candidate to overcome the

Corresponding author. E-mail addresses: yeyaoyao@ust.hk (Y. Ye), jiang.xu@ust.hk (J. Xu).

0141-9331/\$ - see front matter © 2012 Published by Elsevier B.V. http://dx.doi.org/10.1016/j.micpro.2012.06.010

limitations of traditional metallic-interconnect based electronic NoCs. Regular topologies, such as mesh and torus, are attractive for NoC designs because of the simplicity and predictable scalability in terms of performance and power consumption [7–9]. Different from mesh topology, torus takes advantage of the wrap-around links among edge nodes to offer better path diversity and load

Optical NoCs offer a new approach to empowering ultra-high bandwidth with low power consumption. With certain device technologies, the power efficiency of the optical NoC is mainly governed by the optical power loss that is encountered by the light signals along the path. A large number of waveguide crossings in an optical transmission path would result in significant optical power loss. To minimize power loss in optical NoCs, it is desired to reduce the number of waveguide crossings within the whole network. The subject of this work is the analytical analysis of important characteristics of mesh and torus topologies based optical NoCs. The study covers important design metrics for optical NoCs, such as the number of waveguide crossings in the floorplan and the number of paths and hops. We summarize the results into equations, taking all the dimensional cases into consideration. Based on the study, as well as the properties of the XY routing algorithm, we propose better floorplans than the existing solutions by reducing the number of waveguide crossings in the network. In our terminology,

the network topology is logical topology, which refers to the logical connections between nodes. It does not give information about the actual physical layout of the network. Floorplan refers to the exact physical arrangement of nodes and their connecting links in the network. There can be many different floorplans for the same topology. In this work, we optimized the physical floorplan for torusbased optical NoCs by carefully arranging waveguides and I/O ports of optical routers. The floorplan optimization reduces the total number of waveguide crossings within the whole floorplan, as well as the number of waveguide crossings in longest paths. Comparison results show that the optimized floorplans of torus-based optical NoCs have less waveguide crossings than the original designs, regarding whether the total number of waveguide crossings within the whole floorplan or the number waveguide crossings in longest paths. Since the number of waveguide crossings affects the power loss of packet transmitted in the network, the power efficiency of packet transmission is optimized through floorplan optimiza-

The rest of paper is organized as follows. Section 2 and 3 covers the study on mesh and torus networks respectively. In Section 4, several approaches are proposed to optimize the floorplan of torus-based ONoCs. The optimized flooprlans are evaluated by comparing with the original designs in terms of the number of waveguide crossings. Section 5 shows the simulation results and analyzes the performance of the optimized floorplans. Section 6 concludes the paper.

### 2. Related work

Several on-chip optical interconnection networks have been proposed based on mesh or torus topologies. Shacham et al. proposed a circuit-switched augmented folded torus network interconnected by  $4 \times 4$  optical switches [10]. Gu et al. proposed a mesh-based optical NoC with low power loss and cost [11]. In order to facilitate local traffic, some photonic NoC architectures are designed to utilize electrical interconnect for fast local switching. Batten et al. proposed an optical NoC with global crossbar topology, where processing cores and DRAM are divided in sub-mesh and connected with a hybrid opto-electrical global optical crossbar [12]. Vantrease et al. proposed a clustered optical interconnection network Corona, with broadcasting support [13]. Pan et al. proposed two novel optical architectures for global communication, including Firefly [14] and a further improved architecture Flexishare [15]. Mo et al. proposed a hierarchical hybrid optical-electronic NoC based on mesh topology [16]. Kirman et al. proposed a hierarchical opto-electrical system, where an optical ring with WDM support is used to connect electronic clusters [17]. Ouyang et al. proposed a quality-of-service framework for optical NoCs based on frame-based arbitration [18]. Le Beux et al. presented a contention-fee optical ring NoC (ORNoC) [19]. Zhang et al. proposed a torus-based optical NoC architecture GTON-XII, where data are transmitted in packet switching with multiple wavelengths [20]. Ye et al. systematically modeled and quantitatively analyzed the thermal effects in optical NoCs [21].

In optical NoCs, waveguide crossings introduce insertion loss for passing signals. Although the insertion loss per waveguide crossing is small (about 0.12 dB [22]), a large number of crossings in the optical path may lead to significant power loss. To improve the power loss in optical NoCs, it is desired to reduce the number of waveguide crossings within the whole network. This can be done by improving the structure of optical routers. Low-loss optical routers with reduced number of waveguide crossings inside the switching fabric were proposed in [23,24]. This work is based on

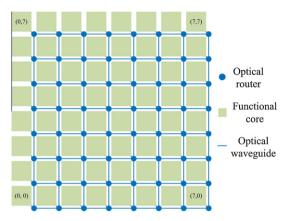

Fig. 1. An  $8 \times 8$  2D mesh-based optical NoC.

the optimized non-blocking routers proposed in [24], which has the least power loss than other router designs so far. Besides the optimization of optical router structures, some research work has also been done on the network topology in order to improve the insertion loss. Chan et al. [25] proposed improved topology for the torus network proposed in [10]. The improved topology reduces the overall insertion loss of waveguide crossings. In this work, we present a detailed study on the floorplan of mesh and torus-based optical NoCs. We provide equations serving as tools to evaluate the characteristics and performance of mesh and torus-based ONoCs in terms of the numbers of paths, hops, and waveguide crossings. All kinds of dimensional conditions of the networks have been taken into consideration during analysis. For torus networks, both the unfolded and folded scenarios are analyzed. Based on this study, as well as the properties of the XY routing algorithm, we propose several approaches to optimize the power efficiency of optical NoCs by minimizing the number of waveguide crossings in the floorplan.

# 3. Mesh floorplan analysis

# 3.1. Mesh path analysis

An  $8 \times 8$  2D mesh-based ONoC is shown in Fig. 1. For a packet transmission in an  $M \times N$  mesh, we define the coordinates of the source to be  $(x_i, y_i)$ , the coordinates of the packet destination to be  $(x_j, y_j)$ , with  $x_i, x_j \in [1]$  and  $y_i, y_j \in [1]$ . The route each packet takes from the source to the destination is defined as a path. We use XY routing (two-dimensional order routing) for path selection in mesh and torus-based ONoCs [26]. It is a low-complexity distributed algorithm without any routing table, and is particularly suitable for mesh or torus networks. Each packet is routed first in X dimension until it reaches the node in the same column with the destination, and then along the perpendicular Y dimension to the destination. Destination address is the only information required to find the next hop on a path. This simplicity reduces the control logic of the router, and helps reduce the energy consumed by routers for routing decisions.

The total number of possible paths with XY routing in the  $M \times N$  mesh is  $N_{path} = MN(MN-1)$ . For each router, along its X and Y directions, there are M+N-2 different paths without any turning. Hence for all the  $M \times N$  routers in the mesh, the number of paths with no turning is  $N_{path\_no\_turn} = MN(M+N-2)$ .

In a path, every step takes from one router to the next is defined as a hop. The total number of hops in all possible paths is shown in Eq. (1).

$$H = \sum_{x_i=1}^{M} \sum_{x_j=1}^{M} \sum_{y_i=1}^{N} \sum_{y_j=1}^{N} (|x_i - x_j| + |y_i - y_j|)$$

$$= N^2 \sum_{x_i=1}^{M} \sum_{x_j=1}^{M} |x_i - x_j| + M^2 \sum_{y_i=1}^{N} \sum_{y_j=1}^{N} |y_i - y_j|$$

$$= 2N^2 \sum_{k=1}^{M-1} (kM - k^2) + 2M^2 \sum_{k=1}^{M-1} (kN - k^2)$$

$$= MN(MN - 1)(M + N)/3$$

(1)

It can be found that there are 2 k pairs of  $x_i$  and  $x_j$  which are M-k hops apart from each other, with k=1, 2, ..., M-1. For instance, there are four pairs of  $x_i$  and  $x_j$  that it takes them M-2 hops to reach each other. This principle also holds for  $y_i$  and  $y_j$  in vertical direction. By applying this principle, Eq. (1) is simplified. Then we obtain the average number of hops in a path is  $H_{ave} = (M+N)/3$ .

## 3.2. Mesh loss analysis

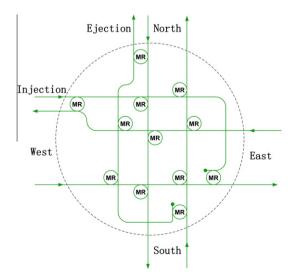

Different types of power loss shall exist in an optical path in optical NoCs. One major type is the loss induced within an optical router. Fig. 2 shows the optimized non-blocking OXY optical router [24]. The five bidirectional ports include injection/ejection, east, south, west and north ports. They are aligned to their intended directions so that no extra waveguide crossing will be incurred in the floorplan. Input and output of each port are also properly aligned. The injection/ejection ports are used to connect the optical/electronic (O/E) interface. Conversions between electronic and optical domains are facilitated by the O/E interface, which handles serialization, O/E conversions and deserialization. Microresonators are used in the router to perform the switching function. As shown in Fig. 2, each microresonator is coupled to two waveguides. Microresonators has different on-state and off-state resonance wavelengths. If the input light has the same wavelength with the microresonator, it would be coupled into the microresonator and directed to the other waveguide. Otherwise, the light would propagate directly along the input waveguide. Multiple microresonators are combined together in the router to implement the  $5 \times 5$ switching function. By turning on or off microresonators properly, the injected optical signal can be controlled to propagate from an input port to an output port. When a light passes through the router, optical power loss would be induced by the microresonators

Fig. 2. Port structure of OXY optical router.

and waveguide crossings in the path. For a microresonator fabricated based on silicon waveguide with cross-section  $500 \times 200$  nm, the insertion loss is about 0.5 dB [27]. Each waveguide crossing introduces about 0.12 dB insertion loss to the passing optical signals [28]. In current technology, waveguide propagation loss is about 0.17 dB/mm [29]. Table 1 shows the optical power loss when the light signal passes through the OXY router. We use alphabetical letters as subscripts to represent the input/output ports of the routers. For example,  $L_{InE}$  represents the optical power loss from the Injection port to the East port.  $L_{SEj}$  represents the optical power loss from the West port to the East port.  $L_{SEj}$  represents the optical power loss from the South port to the Ejection port. We use  $L_W$  to represent the waveguide propagation loss within one hop.

The longest paths refer to the paths that take M+N-2 hops in an  $M\times N$  mesh with XY routing algorithm. There are particularly four such paths:  $\to \uparrow$ ,  $\uparrow \leftarrow$ ,  $\to \downarrow$ ,  $\downarrow \leftarrow$ . By taking the average of loss in these four paths, we can obtain the average loss in the longest paths in

$$L = (M + N - 2)L_W + [2(M - 2)(L_{WE} + L_{EW}) + 2L_{InE} + 2L_{InW}$$

$$+ L_{WN} + L_{EN} + L_{WS} + L_{ES} + 2(N - 2)(L_{SN} + L_{NS}) + 2L_{SEj}$$

$$+ 2L_{NFi}/4$$

(2)

Suppose K = MN, Eq. (2) can be transformed to Eq. (3). As different losses going through a router are generally close to each other, we approximate them into a common term  $L_0$ . c is a constant

$$\begin{split} L &= (M + K/M - 2)L_W + [4L_0(M + K/M - 4) + L_{ES} + 2L_{SEj} \\ &+ 2L_{InE} + 2L_{InW} + L_{WN} + L_{EN} + L_{WS} + 2L_{NEj}]/4 \\ &= (M + K/M - 2)L_W + (M + K/M - 4)L_0 + c \end{split} \tag{3}$$

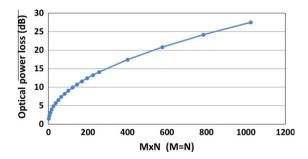

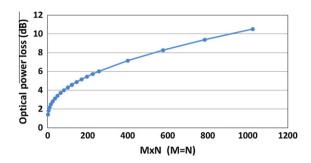

The average loss in the longest paths in Eq. (3) is minimized when  $M = N = K^{0.5}$ ) = a. The result of the minimum is shown in Eq. (4) and Fig. 3

$$L = (2a - 2)L_W + [2L_{InE} + 2L_{InW} + L_{WN} + L_{EN} + L_{WS} + L_{ES} + 2(a - 2)(L_{WE} + L_{EW} + L_{SN} + L_{NS}) + 2L_{SEj} + 2L_{NEj}]/4$$

(4)

We divide the average loss in paths into Eqs. (5)–(7) in order to make the calculation less complex.  $L_{ln}$  represents the average optical power loss when the light is injected to the first router.  $L_{WG}$  represents the average waveguide propagation loss along the path.  $L_{RT}$  represents the average optical power loss in all the intermediate routers in the path.  $L_{Ej}$  represents the optical power loss when the light is ejected by the last router at the destination

$$L_{ln} = (2L_{lnW} + 2L_{lnE} + L_{lnN} + L_{lnS})/6$$

(5)

$$L_{WG} = (M+N)L_W/3 \tag{6}$$

$$L_{RT} = (P_0 + H_{ave} - 2) \cdot \frac{L_{WE} + L_{EW} + L_{NS} + L_{SN}}{4} + (1 - P_0) \cdot \frac{L_{WN} + L_{EN} + L_{WS} + L_{ES}}{4}$$

(7)

$$L_{Ej} = (2L_{NEj} + 2L_{SEj} + L_{WEj} + L_{EEj})/6$$

(8)

**Table 1**Loss (in dB) when passing through a router using different *I/O* ports.

| I/O Port  | North | West | South | East | Ejection |

|-----------|-------|------|-------|------|----------|

| North     | NA    | 1.05 | 0.48  | 1.04 | 0.5      |

| West      | 0.98  | N.A. | 0.74  | 0.36 | 0.74     |

| South     | 0.36  | 1.54 | NA    | 1.22 | 0.98     |

| East      | 0.74  | 0.48 | 0.98  | NA   | 0.98     |

| Injection | 0.74  | 0.5  | 0.98  | 0.98 | NA       |

Fig. 3. Minimum average loss in longest paths.

In Eq. (7),  $P_0$  is the probability that the path has no turning. Assuming each path has equal chance to be taken by the packets,  $P_0$  can be calculated as

$$P_0 = \frac{N_{path\_no\_turn}}{N_{path}} = (M+N-2)/(MN-1) \eqno(9)$$

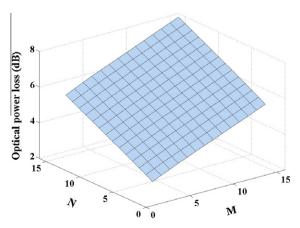

By summing up all the partial losses, we can obtain the average loss in a path as in Eq. (10). Similar to our previous discussions, by substituting M with K/N, we can have Eq. (10), where c is a constant. Fig. 4 is a three-dimensional plot showing the loss in dB by specifying the losses shown in Table 1

$$\begin{split} L_{Ave} &= L_{In} + L_{Ej} + L_{WG} + L_{RT} \\ &= \left[ (K+2)(L_{WE} + L_{EW} + L_{NS} + L_{SN}) + 4(K-1)L_W - 3(L_{WN} + L_{EN} + L_{WS} + L_{ES}) \right] \cdot \frac{N + K/N}{12(MN-1)} + c \end{split} \tag{10}$$

Assuming  $K \gg 1$ , it is very likely that (K+2)  $(L_{WE} + L_{EW} + L_{NS} + L_{SN}) - 3(L_{WN} + L_{EN} + L_{WS} + L_{ES}) + 4(K-1)L_W > 0$ , since different losses going through a router are close to each other. Based on this assumption, the minimum average loss could be achieved by minimizing the term N + K/N when  $M = N = K^{0.5} = a$ , as shown in Eq. (11) and Fig. 5.

$$\begin{split} L_{Ave} &= \frac{L_{InW} + L_{InE} + L_{SEj} + L_{NEj} + 2aL_W}{3} \\ &+ \frac{a(a-2)(L_{WE} + L_{EW} + L_{NS} + L_{SN})}{6(a+1)} \\ &+ \frac{(a-1)(L_{WN} + L_{EN} + L_{WS} + L_{ES})}{4(a+1)} \\ &+ \frac{L_{InN} + L_{InS} + L_{WEj} + L_{EEj}}{6} \end{split}$$

**Fig. 4.** Average optical power loss in paths in  $M \times N$  2D mesh.

Fig. 5. Minimum average loss in paths.

# 4. Torus floorplan analysis

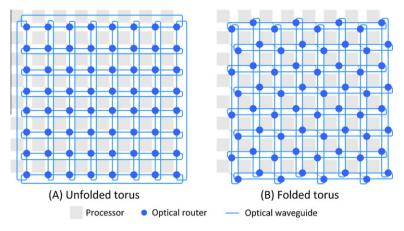

Torus topology (Fig. 6) are attractive because of the better path diversity than mesh. Similar to our previous discussions on mesh-based optical NoCs, we define the coordinates of the packet source to be  $(x_i, y_i)$ , the coordinates of the packet destination to be  $(x_j, y_j)$ , with  $x_i, x_j \in [1]$  and  $y_i, y_j \in [1]$ . Compared with the unfolded torus, folded torus achieves more balanced hop latency and avoids extra energy consumption in the wrap-around channels. For the analysis in this section, the unfolded torus and folded torus should have the same results in the analysis of the number of hops or paths.

# 4.1. Number of hops

We have already got the number of hops in all possible paths in an  $M \times N$  mesh-based optical NoC with XY routing (Eq. (1)). To calculate the total number of hops in all possible paths in an  $M \times N$  torus network, we could simply deduct the number of hops that are reduced by the torus structure from the total number of hops in the  $M \times N$  mesh.

# 4.1.1. When both M and N are odd

The number of hops that are reduced by the torus structure is the sum of the hops reduced in X dimension and in Y dimension. When both M and N are odd, the number of hops that are reduced in X dimension is shown in Eq. (12), and the number of hops that are reduced in Y dimension is shown in

$$X = 2[(M-1)-1] + 4[(M-2)-2] + \dots + (M-1)[(M+1)/2 - (M-1)/2]$$

=  $M(M^2 - 1)/12$  (12)

$$Y = N(N^2 - 1)/12 (13)$$

Then the total number of hops in  $M \times N$  torus is calculated in

$$H = \frac{MN(MN-1)(M+N)}{3} - N^2X - M^2Y$$

$$= \frac{MN^2(M^2-1) + M^2N(N^2-1)}{4}$$

(14)

# 4.1.2. When M is even and N is odd

In  $M \times N$  torus, when the number of routers in a dimension is even, there would be cases where two paths between a pair of routers have the same number of hops. To be specific, if the number of routers in a dimension is k which is even, the number of extra paths within this dimension alone is also k, when compared to the mesh with the same network size. When M is even and N is odd, the number of hops that are reduced in X dimension is as in Eq. (15), whereas in the Y dimension the result is the same as in the previous case (Eq. (13)).

Fig. 6. Torus topology.

$$X = 2[(M-1)-1] + 4[(M-2)-2] + \dots + (M-2)[(M+1)/2 - (M-1)/2]$$

=  $M(M^2 - 4)/12$  (15)

For each router, where the extra paths change directions, the expression of the number of extra hops  $H_{ex}$  is obtained in Eq. (16).

$$H_{ex} = (2M + N + 1)(N - 1)/4 + M/2 \tag{16}$$

Then the total number of hops is calculated in

$$\begin{split} H &= \frac{MN(MN-1)(M+N)}{3} + MNH_{ex} - N^2X - M^2Y \\ &= \frac{MN(MN^2 + M^2N - M + 2MN + N^2 - 1)}{4} \end{split} \tag{17}$$

# 4.1.3. When both M and N are even

When both *M* and *N* are even, by applying similar methods, the expression of the total number of hops is shown in

$$H = \frac{MN((M+N)(MN+M+N+2)+2MN)}{4} \tag{18}$$

# 4.2. Number of paths

For  $M \times N$  mesh, the number of paths that are uniquely determined by the XY routing algorithm is as Eq. (1). For  $M \times N$  torus, when the number of routers in a dimension is even, there would be cases where two paths between a pair of routers have the same number of hops. To be specific, when the number of routers in a dimension is k which is even, the number of extra paths within this dimension alone is also k. Table 2 shows the total number of possible paths in a  $M \times N$  torus with XY routing. For a router in  $M \times N$  mesh, there are M-1 and N-1 different paths in its corresponding X and Y directions without turning. For torus network with the same size, when M or N is an even number, there would be one extra path for each router. Hence for all the MN routers in torus, the number of paths without turning can be obtained as in Table 2.

**Table 2** The number of paths in  $M \times N$  torus with XY routing.

|                     | N <sub>path</sub> | N <sub>path_no_turn</sub> |

|---------------------|-------------------|---------------------------|

| M, N are odd        | MN(MN-1)          | MN(M+N-2)                 |

| M is even, N is odd | $MN(MN-1) + MN^2$ | MN(M+N-1)                 |

| M, N are even       | MN(MN+M+N)        | MN(M+N)                   |

# 4.3. Average number of hops in a path

The average number of hops in a path can be simply obtained by dividing the total number of hops in all possible paths by the total number of paths.

When both M and N are odd

$$H_{ave} = \frac{MN^2(M^2 - 1) + M^2N(N^2 - 1)}{4MN(MN - 1)} = \frac{M + N}{4}$$

(19)

When M is even and N is odd

$$H_{ave} = \frac{MN^2 + M^2N - M + 2MN + N^2 - 1}{4MN(MN + N - 1)}$$

(20)

When both M and N are even

$$H_{ave} = \frac{(M^2 + 2M)(N+1) + (N^2 + 2N)(M+1)}{4MN(MN+M+N)} \tag{21}$$

# 4.4. Number of hops in longest paths

In  $M \times N$  mesh with XY routing, it takes M+N-2 hops in each longest path. In torus with the same network size, the number of hops in a longest path is reduced by the wrap-around links between edges routers. When both M and N are odd, the number of hops in a longest path is (M+N)/2-1; when M is even and N is odd, the number of hops in a longest path is (M+N)/2-0.5; when both M and N are even, the number of hops in a longest path is (M+N)/2.

# 5. Torus network optimizations

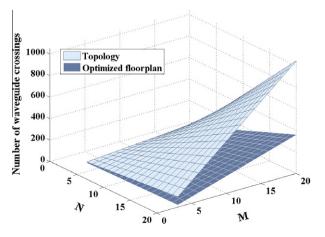

With certain device technologies, the power efficiency of optical NoC is mainly governed by the optical power loss that is encountered by the light signals along the path. Waveguide crossings in optical NoCs do not affect the bandwidth, but cause more loss and power consumption during packet transmission. Each waveguide crossing introduces about 0.12 dB insertion loss to the passing optical signals [28]. To minimize power loss in optical NoCs, it is desired to reduce the number of waveguide crossings within the whole floorplan. However, the topology of an optical NoC may not directly indicate the optimal physical floorplan. In order to reduce waveguide crossings in the network level, we optimize the floorplans for both the unfolded and folded torus-based optical NoCs by rearranging the waveguides and I/O ports of the optical routers. The optimized floorplans maintain the connection property showed in the unfolded and folded torus topologies, but minimize

the number of waveguide crossings in physical implementations. The floorplan optimization targets general applications. It reduces the number of waveguide crossings within the whole floorplan, as well as the number of waveguide crossings in the longest paths. The optimization is applicable to torus-based optical NoCs with any task mapping and traffic patterns. And the optimized floorplans can be directly used to physically implement a torus-based optical NoC on a chip.

# 5.1. Unfolded torus optimizations

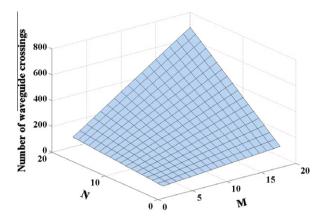

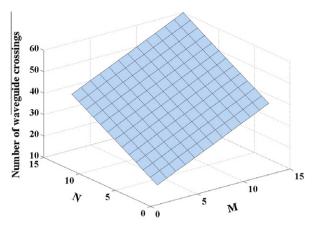

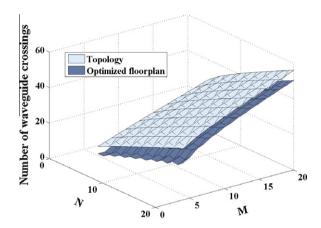

In  $M \times N$  unfolded torus topology (Fig. 6), the total number of waveguide crossings within the whole network is 3MN - 4M - 4N + 8. One method to reduce the waveguide crossing is by rearranging optical waveguides. There could be multiple ways to rearrange the waveguides, but with the same crossing reduction effects. For all the cases in an  $M \times N$  unfolded torus, after the optimization, the minimum number of total crossings is reduced to MN. The network can be further optimized by switching the I/O ports of the optical routers and the minimum number of total crossings becomes  $MN - 2 \cdot max(M, N)$ .

Fig. 7 and Fig. 8 show that waveguide crossings in the unfolded torus-based optical NoC are reduced effectively through floorplan optimization. In an  $8 \times 8$  unfolded torus-based optical NoC, the total waveguide crossings number in the topology is 136, and the optimized floorplan reduces it to 48. The reduction can be even more effective when M and N are getting large. In an  $16 \times 16$  unfolded torus-based optical NoC, the total waveguide crossings number in the topology is 648, and the optimized floorplan reduces it to 224

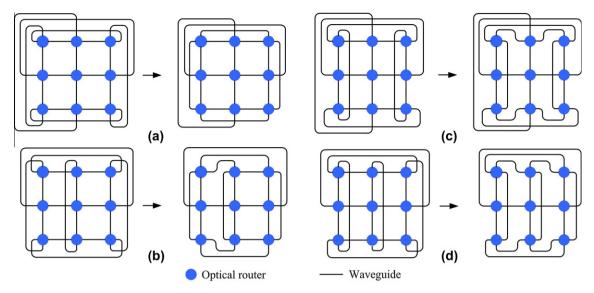

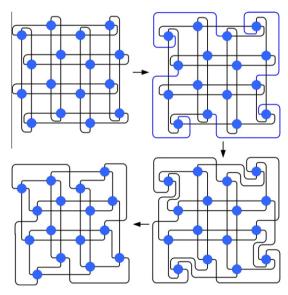

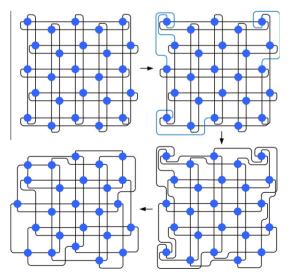

To better illustrate the optimization methods, we consider all possible floorplans and find the optimized one with the minimum number of waveguide crossings. When M and N are both odd, the optimization method is shown in Fig. 9, where (a)-(d) are four possible cases for a  $3 \times 3$  unfolded torus. We find that the minimum number of waveguide crossings in the  $3 \times 3$  unfolded torus is 3(figure b-d). When M is even and N is odd, the optimizations for different possible structures are illustrated in Fig. 10 with the  $4 \times 3$  unfolded torus as examples. In this case, the minimum number of waveguide crossings is 4 (figure a and e). When both M and N are even, the optimization method is illustrated in Fig. 11, with the  $4 \times 4$  unfolded torus as examples. We find that the optimized floorplans (figure b and c) have eight waveguide crossings, which is the minimum in all the possible four floorplans. After the optimization, the change in network area is negligible. The longest waveguide is nearly half of the chip perimeter, and the corresponding

Fig. 7. The total number of waveguide crossings in  $M \times N$  unfolded torus-based optical NoC.

**Fig. 8.** The number of waveguide crossings reduced by floorplan optimization in  $M \times N$  unfolded torus-based optical NoC.

latency is about 0.232 ns (assuming that the chip size is  $10 \times 10$  mm, the refractive index of the waveguide is 3.48). Since the 0.232 ns latency in the longest waveguide is well within one clock cycle (0.8 ns, assume that the electronic part of the optical NoC works at 1.25 GHz), the performance would not be affected by the floorplan optimization. Compared with the unfolded torus, the folded torus achieves more balanced link latency.

### 5.2. Folded torus optimizations

The methods of floorplan optimization for folded torus are similar to those of unfolded torus. In order to compare the loss performance between the original topology and the optimized floorplan, we will analyze the total number of waveguide crossings within the whole network and the number of waveguide crossings in the longest paths. Different longest paths may have different number of waveguide crossings. We will give the maximum number of waveguide crossings that are possible in longest paths, as well as the average number of waveguide crossings in longest paths. For the folded torus, we find that the number of waveguide crossings depends on not only *M* and *N* but also their parities due to different network arrangements. Table 3 summarizes the total number of waveguide crossings in the original topology and the optimized floorplan. Table 4 summarizes the maximum number of waveguide crossings in longest paths.

# 5.2.1. When both M and N are even

In the original design of the folded torus structure, which is illustrated in Fig. 6B, the total number of waveguide crossings in the whole network is 3MN - 2M - 2N. In this network, there are many longest paths as we have previously defined. Among these paths, we can find one or several which have the most waveguide crossings. A longest path may have 1.5(M+N)-2 waveguide crossings at most. Next we will analyze the average number of waveguide crossings in longest paths under different conditions. For any router in the folded torus that is acting as the packet sender, we can always find at least one longest path. When there are multiple choices of the longest path, we can always choose the one with the most waveguide crossings. Here we define this behavior as the worst case. On the other hand, we can also choose the longest path with the least number of waveguide crossings, and define this behavior as the best case. When all the possible longest paths are taken into consideration, we can then calculate the average number of waveguide crossings in the longest paths within this network. For consistency, we would like to define the result as the average case.

Fig. 9. Optimizations for a  $3 \times 3$  2D unfolded torus with four different possible structures.

Fig. 10. Optimizations for a  $4 \times 3$  2D unfolded torus with seven different possible structures.

We divide the calculations for the average number of waveguide crossings in longest paths in the worst or best cases further into sub-cases under different dimensional conditions: when both M/2 and N/2 are even numbers, or when M/2 is even and N/2 is odd, or when both M/2 and N/2 are odd numbers. The results for the worst cases are shown in Eq. (22), Eq. (23), and Eq. (24) correspondingly

$$C_{w1} = \frac{3MN(M+N) - (M^2 + N^2)}{2MN} - 2 \tag{22}$$

$$C_{w2} = \frac{3MN(M+N) - (M^2 + N^2 - 4)}{2MN} - 2 \tag{23}$$

$$C_{w2} = \frac{3MN(M+N) - (M^2 + N^2 - 4)}{2MN} - 2$$

$$C_{w3} = \frac{3MN(M+N) - (M^2 + N^2 - 8)}{2MN} - 2$$

(23)

Please cite this article in press as: K. Feng et al., A formal study on topology and floorplan characteristics of mesh and torus-based optical networks-onchip, Microprocess. Microsyst. (2012), http://dx.doi.org/10.1016/j.micpro.2012.06.010

**Fig. 11.** Optimizations for a  $4 \times 4$  2D unfolded torus with four different possible structures.

Table 3 The total number of waveguide crossings in an  $M \times N$  folded torus.

|                                                | Original topology                                          | Optimized floorplan                                  |

|------------------------------------------------|------------------------------------------------------------|------------------------------------------------------|

| M, N are even M is odd, N is even M, N are odd | 3MN - 2(M + N)<br>3MN - 2(M + N) + 2<br>3MN - 2(M + N) + 2 | 3MN - 4(M+N)<br>3MN - 4(M+N) + 2<br>3MN - 4(M+N) + 2 |

Table 4 The maximum number of waveguide crossings in longest paths.

|                     | Original topology | Optimized floorplan |

|---------------------|-------------------|---------------------|

| M, N are even       | 1.5(M+N)-2        | 1.5(M+N)-4          |

| M is odd, N is even | 1.5(M+N)-2.5      | 1.5(M+N)-5.5        |

| M, N are odd        | 1.5(M+N)-3        | 1.5(M+N)-7          |

The results for the best cases are presented in Eq. (25), Eq. (26), and Eq. (27) correspondingly for different dimensional conditions.

$$C_{b1} = \frac{3MN(M+N) - 3(M^2 + N^2)}{2MN} - 2 \tag{25} \label{eq:cb1}$$

$$C_{b2} = \frac{3MN(M+N) - 3(M^2 + N^2) - 4}{2MN} - 2 \tag{26}$$

$$C_{b2} = \frac{3MN(M+N) - 3(M^2 + N^2) - 4}{2MN} - 2$$

$$C_{b3} = \frac{3MN(M+N) - 3(M^2 + N^2) - 8}{2MN} - 2$$

(26)

The average case can be calculated as Eq. (28).

$$C_{ave} = \frac{3MN(M+N) - 2(M^2 + N^2)}{2MN} - 2 \tag{28}$$

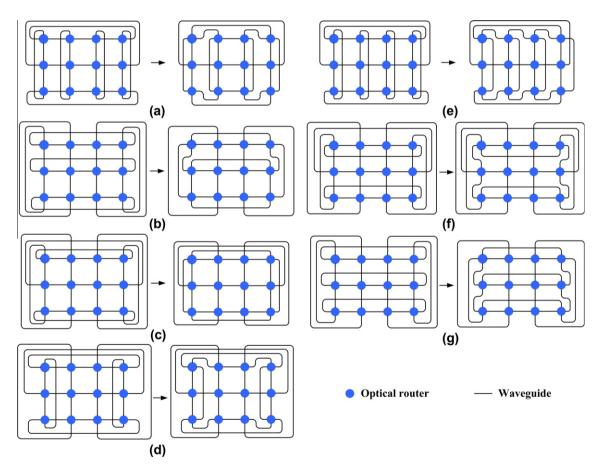

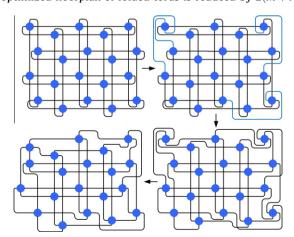

The methods of floorplan optimization for the folded torus are the same as those applied to optimize the unfolded torus networks. As shown in Fig. 12, some optical waveguides between the routers are rearranged, and then the *I*/*O* ports of the routers (particularly. the routers on the boundaries) are switched. Optical waveguides are further rearranged in the last step, where there is no waveguide crossing reduction involved. However, this step is necessary not only because it makes the whole floorplan neat, but because it eliminates extra waveguide bending loss induced by the previous port switching.

The following analysis is similar to our previous discussions. The total number of waveguide crossings in the optimized floor-

Fig. 12. Optimization procedure for a  $4 \times 4$  2D folded torus.

plan of the  $M \times N$  folded torus network is reduced by 2(M + N)to 3MN - 4M - 4N. The maximum number of waveguide crossings that are possible in longest path is reduced to 1.5(M + N) - 4.

For the average number of waveguide crossings in longest paths in the worst case, Eqs. (29)-(31) are the results corresponding to different dimensional conditions: when both M/2 and N/2 are even numbers, when M/2 is even and N/2 is odd, and when both M/2 and N/2 are odd numbers

$$C_{w1} = \frac{3MN(M+N) - 4(5M+5N-12)}{2MN} - 4 \tag{29}$$

$$C_{w2} = \frac{3MN(M+N) - 4(5M+6N-12)}{2MN} - 4 \tag{30}$$

$$C_{w3} = \frac{3MN(M+N) - 4(6M+6N-12)}{2MN} - 4 \tag{31}$$

Eqs. (32)–(34) are the average number of waveguide crossings in longest paths in the best case

$$C_{b1} = \frac{3(M+N)}{2} - \frac{2(M^2+N^2) - 6(M+N) - 8}{MN} - 8$$

(32)

$$C_{b2} = \frac{3(M+N)}{2} - \frac{2(M^2+N^2) - 6M - 4N - 8}{MN} - 8$$

$$C_{b3} = \frac{3(M+N)}{2} - \frac{2(M^2+N^2) - 4(M+N) - 8}{MN} - 8$$

(33)

$$C_{b3} = \frac{3(M+N)}{2} - \frac{2(M^2+N^2) - 4(M+N) - 8}{MN} - 8 \tag{34}$$

The average number of waveguide crossings in longest paths is

$$C_{ave} = \frac{(3MN + 8)(M + N) - 4(M^2 + N^2)}{2MN} - 6 \tag{35}$$

# 5.2.2. When M is odd and N is even

In the original structure of a  $M \times N$  folded torus, when M is odd and N is even, the total number of waveguide crossings in the whole network is 3MN - 2M - 2N + 2. The maximum number of waveguide crossings that are possible in longest path is 1.5(M+N)-2.5.

In order to obtain the average number of waveguide crossings in longest paths, we also divide the calculations for the worst cases and the best cases into more detailed cases, based on different dimensional conditions. However, when performing the case division this time, we only need to consider the Y dimension, which has an even number of routers. In the worst cases, Eq. (36) and Eq. (37) show the results respectively for N/2 is even or odd.

$$C_{w1} = \frac{3(M+N)-7}{2} - \frac{2M^2 + N^2 - 4M - 2N}{2MN}$$

$$C_{w2} = \frac{3(M+N)-7}{2} - \frac{2M^2 + N^2 - 4M - 14N - 6}{2MN}$$

(36)

$$C_{w2} = \frac{3(M+N) - 7}{2} - \frac{2M^2 + N^2 - 4M - 14N - 6}{2MN}$$

(37)

On the other hand, the corresponding results for the best cases are shown in

$$C_{b1} = \frac{3(M+N)-7}{2} - \frac{2M^2 + 3N^2 - 4M - 4N - 6}{2MN}$$

$$C_{b2} = \frac{3(M+N)-7}{2} - \frac{2M^2 + 3N^2 - 4M - 6N + 6}{2MN}$$

(38)

$$C_{b2} = \frac{3(M+N) - 7}{2} - \frac{2M^2 + 3N^2 - 4M - 6N + 6}{2MN}$$

(39)

The average number of waveguide crossings in longest paths is presented in

$$C_{ave} = \frac{3(M+N)}{2} - \frac{M^2 + N^2 - M + N}{MN} - 2 \tag{40} \label{eq:40}$$

The same floorplan optimization methods are applied to the folded torus. The optimization procedures for a  $5 \times 4$  folded torus are shown in Fig. 13. The total number of waveguide crossings in the optimized floorplan of folded torus is reduced by 2(M+N) to

**Fig. 13.** Optimization procedure for a  $5 \times 4$  2D folded torus.

3MN - 4M - 4N + 2. The number of waveguide crossings in longest path that has the most waveguide crossings among all the paths is 1.5(M + N) - 5.5.

For the average number of waveguide crossings in longest paths in the worst cases, Eqs. (41) and (42) show the results for N/2 is even or odd

$$C_{w1} = \frac{3(M+N) - 11}{2} - \frac{6M^2 + 3N^2 - 8M - 8N + 8}{2MN}$$

(41)

$$C_{w1} = \frac{3(M+N) - 11}{2} - \frac{6M^2 + 3N^2 - 8M - 8N + 8}{2MN}$$

$$C_{w2} = \frac{3(M+N) - 11}{2} - \frac{6M^2 + 3N^2 - 8M - 8N + 18}{2MN}$$

(41)

On the other hand, the corresponding results in the best cases are shown in

$$C_{b1} = \frac{3(M+N)-11}{2} - \frac{4M^2 + 5N^2 - 6M - 6N - 6}{2MN}$$

$$C_{b2} = \frac{3(M+N)-11}{2} - \frac{4M^2 + 5N^2 - 6M - 6N - 10}{2MN}$$

(43)

$$C_{b2} = \frac{3(M+N) - 11}{2} - \frac{4M^2 + 5N^2 - 6M - 6N - 10}{2MN}$$

(44)

The average number of waveguide crossings in longest paths is presented in

$$C_{ave} = \frac{3(M+N)-11}{2} - \frac{5M^2+4N^2-15M+7N+18}{2MN} \eqno(45)$$

# 5.2.3. When both M and N are odd

When M and N are odd, the total number of waveguide crossings in a  $M \times N$  folded torus topology is 3MN - 2M - 2N + 2. The number of waveguide crossings in longest path that has the most waveguide crossings among all the paths is 1.5(M+N) - 3.

When M and N are both odd, there is only one longest path for each router as the packet source. Therefore the average number of waveguide crossings in longest paths can be directly obtained in Eq. (46), without any need to further divide the calculations in different sub-cases.

$$C_{ave} = \frac{3(M+N)}{2} - \frac{M^2 + N^2 - 3M - 3N + 2}{MN} - 5 \tag{46}$$

The same floorplan optimization methods are applied to the folded torus network. The optimization procedures for a  $5 \times 5$ folded torus are shown in Fig. 14. The total number of waveguide crossings in the optimized folded torus network is

**Fig. 14.** Optimization procedure for a  $5 \times 5$  2D folded torus

3MN - 4M - 4N + 2. The number of waveguide crossings in the longest path that has the most waveguide crossings among all the paths is 1.5(M + N) - 7.

The average number of waveguide crossings in longest paths is presented in

$$C_{ave} = \frac{3(M+N)}{2} - \frac{2(M^2+N^2) - 5(M-N) + 2}{MN} - 7 \tag{47} \label{eq:cave}$$

# 6. Comparison and analysis

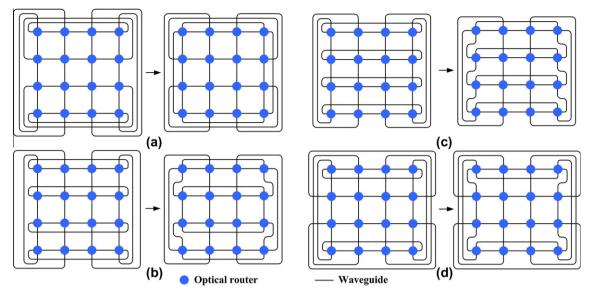

As we analyzed in the above sections, in the original  $M \times N$ folded torus topology, the total number of waveguide crossings is either 3MN - 2(M + N) when both M and N are even numbers, or 3MN - 2(M+N) + 2 otherwise. In the optimized floorplan of  $M \times N$  folded torus network, the total number of waveguide crossings is either 3MN - 4(M + N) when both M and N are even numbers, or 3MN - 4(M + N) + 2 otherwise. The above analysis shows that waveguide crossings in the  $M \times N$  folded torus-based optical NoC can be reduced by 2(M + N) through floorplan optimization. For example, in an  $8 \times 8$  folded torus-based optical NoC, waveguide crossing number in the topology is 160, and the optimized floorplan reduces it to 128. In a  $16 \times 16$  folded torus-based optical NoC, the total number of waveguide crossings in the original topology reaches 704. The floorplan optimization reduces 64 waveguide crossings in total. In order to provide a relatively more intuitive comparison, here we present these results in Fig. 15 and Fig. 16. The floorplan optimization works better for the unfolded torusbased optical NoC, with less waveguide crossings than the folded one. On the other hand, folded torus topology has more balanced hop length than the unfolded one by folding the whole network. This advantage is more obvious in the optimized floorplans. In the optimized unfolded torus-based optical NoC, the longest waveguide is nearly half of the chip perimeter and is much longer than the longest waveguide in the folded one. In current technology, waveguide propagation loss is about 0.17 dB/mm [29]. In a  $10 \times 10 \text{ mm}^2$  chip, the long wrap-around waveguide in the optimized unfolded torus optical NoC will thus induce about 3.4 dB optical power loss for passing signals. So the unfolded and folded torus-based optical NoCs have their own advantage and disadvantage, and there is a trade-off between the waveguide crossings number and the longest waveguide length.

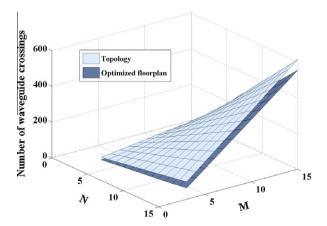

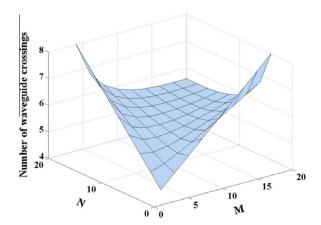

To analyze the number of waveguide crossings in longest paths in folded torus, we have shown equations for different dimension cases. The average number of waveguide crossings in longest paths in  $M \times N$  folded torus is shown in Fig. 17, with M and N ranging from 4 to 20. We can find in Fig. 17 and Fig. 18 that the average number of

**Fig. 15.** The total number of waveguide crossings in  $M \times N$  folded torus-based optical NoC.

**Fig. 16.** The number of waveguide crossings reduced by floorplan optimization in  $M \times N$  folded torus-based optical NoC.

**Fig. 17.** The average number of waveguide crossings in longest paths in  $M \times N$  folded torus-based optical NoC.

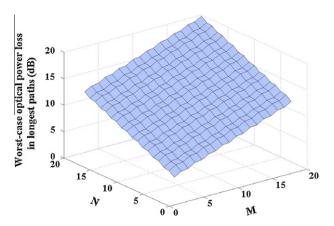

waveguide crossings in longest paths are reduced by the floorplan optimization. The reduction effectiveness depends on the network scale and the parity of M and N. For an  $8 \times 8$  folded torus-based optical NoC, the average number of waveguide crossings are reduced from 20 to 15 after floorplan optimization. For a  $16 \times 16$  folded torus-based optical NoC, the average number of waveguide crossings are reduced from 44 to 38.5 after floorplan optimization. Fig. 19 shows the worst-case power loss in longest paths in  $M \times N$  folded torus after floorplan optimizations. We assume that the waveguide propagation loss per hop is 0.17 dB, and the waveguide

**Fig. 18.** The reduction in waveguide crossings in longest paths through floorplan optimization for  $M \times N$  folded torus.

**Fig. 19.** The worst-case power loss in longest paths in  $M \times N$  folded torus after floorplan optimizaiton.

crossing loss is 0.12 dB. For an 8  $\times$  8 folded torus-based optical NoC with optimized floorplan, the worst-case power loss in longest paths is about 8.62 dB. When the network size increases to 16  $\times$  16, the worst-case power loss is about 16.22 dB.

#### 7. Conclusions

This paper provides a thorough study on the characteristics of mesh and torus-based optical NoCs. Floorplan optimization methods are proposed to reduce the number of waveguide crossings in torus networks. The optimized floorplans of torus-based optical NoCs prove to have less waveguide crossings than the original topology, regarding whether the total number of waveguide crossings within the whole floorplan or the number of waveguide crossings in longest paths. As is suggested in this paper, the number of waveguide crossings represents power loss within the optical NoC. The energy efficiency can be improved through floorplan optimizations.

# Acknowledgement

This work is partially supported by RPC11EG18 and SBI06/07.EG01-4.

# References

- [1] L. Benini, G. DeMicheli, Networks on chip: a new paradigm for systems on chip design, in: Proc. Design, Automation and Test in Europe Conference and Exhibition, 2002, pp. 418–419.

- [2] M. Sgroi, M. Sheets, A. Mihal, K. Keutzer, S. Malik, J. Rabaey, A. Sangiovanni-Vincentelli, Addressing the system-on-a-chip interconnect woes through communication-based design, in: Design Automation Conference. Proceedings, 2001, pp. 667–672.

- [3] G. Martin, Overview of the MPSoC design challenge, in: Design Automation Conference, 43rd ed., ACM/IEEE, 2006, pp. 274–279.

- [4] A. Gerstlauer, D. Gajski, R. Domer, D. Shin, Automatic network generation for system-on-chip communication design, in: CODES+ISSS '05, Third IEEE/ACM/ IFIP International Conference on Hardware/Software Codesign and System Synthesis, 2005, pp. 255–260.

- [5] J. Henkel, W. Wolf, S. Chakradhar, On-chip networks: a scalable, communication-centric embedded system design paradigm, in: Proceedings. 17th International Conference on VLSI Design, 2004, pp. 845–851.

- [6] W. Wolf, A.A. Jerraya, Application-specific system-on-a-chip multiprocessors, IEEE Des. Test 18 (2001) 7.

- [7] T. Bjerregaard, S. Mahadevan, A survey of research and practices of networkon-chip, ACM Comput. Surv. 38 (2006) 1.

- [8] P.P. Pande, C. Grecu, M. Jones, A. Ivanov, R. Saleh, Performance evaluation and design trade-offs for network-on-chip interconnect architectures, IEEE Trans. Comput. 54 (2005) 1025–1040.

- [9] J. Balfour, W.J. Dally, Design tradeoffs for tiled CMP on-chip networks, in: Proc. 20th Annual. Int. Conf. Supercomputing, ACM, New York, NY, USA, 2006, pp. 187–198

- [10] A. Shacham, K. Bergman, L. Carloni, Photonic networks-on-chip for future generations of chip multiprocessors, IEEE Trans. Comput. 57 (2008) 1246– 1260.

- [11] H. Gu, J. Xu, Z. Wang, A novel optical mesh network-on-chip for gigascale systems-on-chip, In: IEEE Asia Pacific Conf. Circuits and Systems, 2008, pp. 1728–1731.

- [12] C. Batten, A. Joshi, J. Orcutt, A. Khilo, B. Moss, C. Holzwarth, M. Popovic, H. Li, H. Smith, J. Hoyt, F. Kartner, R. Ram, V. Stojanovic, K. Asanovic, Building manycore processor-to-DRAM networks with monolithic silicon photonics, in: 16th IEEE Symp. High Performance Interconnects, 2008, pp. 21–30.

- [13] D. Vantrease, R. Schreiber, M. Monchiero, M. McLaren, N. Jouppi, M. Fiorentino, A. Davis, N. Binkert, R. Beausoleil, J. Ahn, Corona: System implications of emerging nanophotonic technology, in: 35th Int. Symp. Computer Architecture, 2008, pp. 153–164.

- [14] Y. Pan, P. Kumar, J. Kim, G. Memik, Y. Zhang, A.Choudhary, Firefly: illuminating future network-on-chip with nanophotonics, in: Proc. 36th Int. Symp. Computer Architecture (ISCA), 2009.

- [15] Y. Pan, J. Kim, G. Memik, Flexishare: channel sharing for an energy-efficient nanophotonic crossbar, in: IEEE 16th Int. Symp. High Performance Computer Architecture, 2010, pp. 1–12.

- [16] K.H. Mo, Y. Ye, X. Wu, W. Zhang, W. Liu, J. Xu, A hierarchical hybrid opticalelectronic network-on-chip, in: Proceedings of the 2010 IEEE Annual Symposium on VLSI, ISVLS110, IEEE Computer Society, Washington, DC, USA, 2010, pp. 327–332.

- [17] N. Kirman, M. Kirman, R. Dokania, J. Martinez, A. Apsel, M.Watkins, D.Albonesi, Leveraging optical technology in future bus-based chip multiprocessors, in: 39th Annual IEEE/ACM Int. Symp. Microarchitecture, pp. 492–503.

- [18] J. Ouyang, Y. Xie, Enabling quality-of-service in nanophotonic network-onchip, in: Design Automation Conference (ASP-DAC) 16th Asia and South Pacific, 2011, pp. 351–356.

- [19] S. LeBeux, J. Trajkovic, I. O'Connor, G. Nicolescu, G. Bois, P. Paulin, Optical ring network-on-chip (ORNoC): architecture and design methodology, in: Design Automation Test in Europe Conference Exhibition (DATE), 2011, pp. 1–6.

- [20] L. Zhang, E. Regentova, X. Tan, A 2d-torus based packet switching optical network-on-chip architecture in: Photonics and Optoelectronics (SOPO) Symposium on, 2011, pp. 1–4.

- [21] Y. Ye, J. Xu, X. Wu, W. Zhang, X. Wang, M. Nikdast, Z. Wang, W. Liu, Modeling and analysis of thermal effects in optical networks-on-chip, in: VLSI (ISVLSI), IEEE Computer Society Annual Symposium on, 2011, pp. 254–259.

- [22] A.W. Poon, F. Xu, X. Luo, Cascaded active silicon microresonator array crossconnect circuits for WDM networks-on-chip, Silicon Photonics III 6898 (2008).

- [23] H. Gu, K.H. Mo, J. Xu, W. Zhang, A low-power low-cost optical router for optical networks-on-chip in multiprocessor systems-on-chip, in: IEEE Computer Society Annual Symp. VLSI, pp. 19–24.

- [24] H.Gu, J.Xu, Z.Wang, A novel optical mesh network-on-chip for gigascale systems-on-chip, in: APCCAS 2008, IEEE Asia Pacific Conference on Circuits and Systems, pp. 1728–1731.

- [25] J. Chan, G. Hendry, A. Biberman, K. Bergman, Architectural exploration of chipscale photonic interconnection network designs using physical-layer analysis, I. Lightwave Technol. 28 (2010) 1305–1315.

- [26] L. Ni, P. McKinley, A survey of wormhole routing techniques in direct networks, Computer 26 (1993) 62–76.

- [27] S. Xiao, M.H. Khan, H. Shen, M. Qi, Multiple-channel silicon micro-resonator based filters for WDM applications, Opt. Express 15 (2007) 7489–7498.

- [28] A.W. Poon, F. Xu, X. Luo, Cascaded active silicon microresonator array crossconnect circuits for WDM networks-on-chip, Silicon Photonics III 6898 (2008).

- [29] F.A. Xia, L.A. Sekaric, Y.T. Vlasov, Ultracompact optical buffers on a silicon chip, Nat. Photonics (2007) 65–71.

**Kai Feng** received his bachelor degree in Electronic Engineering from the Hong Kong University of Science and Technology in 2010. He is currently pursuing the M.A.Sc degree in Electrical Engineering at University of Toronto, Canada

Yaoyao Ye received the B.S. degree in electronic engineering from University of Science and Technology of China, Hefei, China, in 2008. She is currently pursuing the Ph.D. degree in electronic and computer engineering at Hong Kong University of Science and Technology, Hong Kong. Her research focuses on optical networkson-chip for multiprocessor systems-on-chip.

12

Jiang Xu is an Assistant Professor of Department of Electronic and Computer Engineering in the Hong Kong University of Science and Technology. He received his Ph.D. degree from Princeton University in 2007. He received his B.S. and M.S. degrees from Harbin Institute of Technology, China in 1998 and 2000. He was a Research Associate of Bell Labs, from 2001 to 2002, and was a Research Associate of NEC Laboratories America from 2003 to 2005. Jiang Xu was a Member of Technical Staff at a startup company from 2005 to 2007. His research areas include System-on-Chip and Network-on-Chip. Multiprocessor Systems. Low-Power VLSI

on-Chip, Multiprocessor Systems, Low-Power VLSI Design, Nanoelectronic Design, Hardware/Software Codesign, and Embedded Systems.